# NEW MIXER USED IN DIRECT FREQUENCY SYNTHESIZER

#### M. Stork

Department of Applied Electronics and Telecommunications, University of West Bohemia Plzen, 30614 Plzen, Czech Republic, tel.: +420 377624243, mail:stork@kae.zcu.cz

**Summary** Frequency synthesizers are an essential part of any modern transceiver system. They generate clock and oscillator signals needed for up and down conversion. Today's communication standards demand both high frequency accuracy and fast frequency settling. The fine frequency resolution, low spurious signals, accuracy and stability are most important for these devices. In this paper, the new frequency synthesizer architecture based on direct synthesis and coincidence mixer is presented. The simulation results are also shown.

#### 1. INTRODUCTION

Several different frequency synthesis techniques have been presented in the literature over the years. They can be quite clearly divided into three separate categories, namely direct analog synthesis, direct digital synthesis, and indirect analog synthesis. In this context, "indirect" refers to a system based on some kind of a feedback action, whereas "direct" refers to a system having no feedback. One of the most frequently used indirect synthesizer types is the phase-locked loop (PLL). Phases of two signals, i.e. from an external reference and a feedback signal from an oscillator, are compared in a phase and frequency detector. Any phase difference will be converted into a voltage by means of a charge pump. A succeeding loop filter extracts the DC component of this voltage, which is then used to control the output signal frequency of a voltage controlled oscillator (VCO). A PLL provides high output frequency accuracy at reasonable short settling times [1], [2], [3].

In direct analog synthesizer the frequency resolution is achieved by mixing signals of certain frequencies, and then dividing the resulting frequency down. Theoretically, this process can be repeated arbitrarily many times to achieve a finer frequency resolution. Advantages of the direct analog synthesis are very fast switching times and, in theory, arbitrarily fine frequency resolution. However, this technique requires a very large amount of hardware. Also noise is a problem in direct analog synthesis [4].

An alternative architecture for frequency generation is the direct digital synthesis (DDS), e.g. [5], [6]. The output signal is generated in the digital domain with the help of accumulators and a ROM before it is converted to an analog output signal in a D/A converter. The advantages of direct digital synthesizers are good frequency resolution and very fast settling time while showing low spurious noise. As most of the DDS architecture is digital, a high degree of integration can be achieved. However, the accumulator clock must be faster (at least two times) than the generated output frequency which limits the use of DDS applications [7], [8].

# 2. FINE STEP FREQUENCY SYNTHESIZER

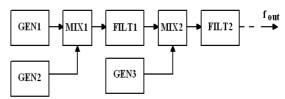

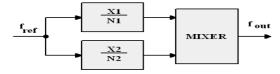

The block diagram of a conventional direct analog frequency synthesizer is shown in Fig. 1.

Fig. 1. The block diagram of a conventional direct analog frequency synthesizer. GEN - generator, MIX - mixer, FILT - bandpass filter.

In this paper frequency synthesizer is based on programmable dividers, multipliers (based on PLL) and coincidence mixers, therefore no filters are need for this synthesizer. For this architecture, Cantor series approximations and Diophantine equations theory are used fine frequency step generation [9]. Let  $N_1$ ,  $N_2$ , ...  $N_k$  be relatively prime positive integers (GCD - Greatest common divisor of  $N_1$ ,  $N_2$ , ...  $N_k$  =1). Then for every integer u, there exist a k integers  $X_1$ ,  $X_2$ , ...  $X_K$ , solving the linear Diophantine equation:

$$\frac{X_1}{N_1} + \frac{X_2}{N_2} + \dots + \frac{X_k}{N_k} = \frac{u}{N_1 N_2 \dots N_k}$$

(1)

If  $N_1$ ,  $N_2$ ,...  $N_k$  are relatively prime positive integers, then for every integer u such that:

$$-N_1 N_2 ... N_k \le u \le N_1 N_2 ... N_k \tag{2}$$

the equation (1) has a solution  $(X_1, X_2, ..., X_K)$ , where that  $-N_i \le X_i \le N_i$  for all i=1,2,...k.

It is important to say, that equation (1) has a k solutions (for  $-N_i \le X_i \le N_i$ ).

Example 1:

$N_1=7$ ,  $N_2=9$ ,  $N_3=11$  and u=1. The solutions of (1) are shown in Tab. 1.:

| $X_1$ | $X_2$ | $X_3$ | Sum |

|-------|-------|-------|-----|

| -6    | 2     | 7     | 89  |

| 1     | -7    | 7     | 99  |

| 1     | 2     | -4    | 21  |

Tab. 1. Example of solution (1) for  $N_1$ =7,  $N_2$ =9,  $N_3$ =11 and u=1. Solution [1, 2, -4] is optimal.

In Tab. 1., numbers in column "**Sum**" are computed according (3)::

$$Sum = \sum_{i=1}^{k} X_{i}^{2}$$

(3)

and optimal value is minimal according eq. (3). Therefore, *Example 1* has 3 solutions:

$(1/7)+(2/9)+(-4/11) = (-6/7)+(2/9)+(7/11) = (1/7)-(7/9)+(7/11) = 1/(7*9*11) = 1.443.10^{-3}$ Example 2:

$N_1$ =7,  $N_2$ =9,  $N_3$ =11 and u=10. The optimal solution of (1) is: [-4, 2, 4] (also [3,-7, 4] and [3, 2,-7]). Optimal values of

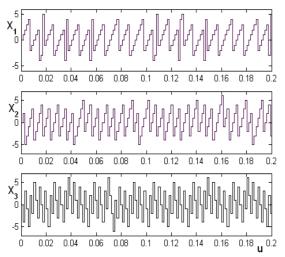

$X_1$ ,  $X_2$ ,  $X_3$  for values  $N_1$ =7,  $N_2$ =9,  $N_3$ =11 and  $u/(N_1 N_2 N_3) = <0$ , 0.2>are shown in Fig. 2.

Fig. 2. Optimal values of  $X_1$ ,  $X_2$ ,  $X_3$  for Example 1 and  $u/(N_1 N_2 N_3) = <0$ , 0.2>

For frequency synthesizer consist of k dividers and multipliers the minimal frequency and minimal frequency step is given by (4):

$$Frequency\_step = \frac{f_{REF}}{\prod_{i=1}^{k} N_i}$$

(4)

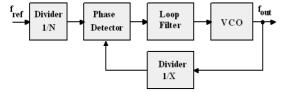

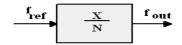

Fig. 3. Block diagram of (X/N) part with PLL

Fig. 4. Simplified block diagram of Fig. 3.

Fig. 5. Block diagram of synthesizer part

For Example 1, Frequency\_step =  $1.443.10^{-3} f_{REF}$ . The hardware implementation part of  $(X_i/N_i)$  is shown in Fig. 3. This can be simplified according Fig. 4. Output frequency is given by (5):

$$f_{OUT} = \frac{X_i}{N_i} f_{REF} \tag{5}$$

Synthesizer part block diagram is shown in Fig. 5. Output frequency is given by (6):

$$f_{OUT} = (\frac{X_1}{N_1} + \frac{X_2}{N_2}) f_{REF}$$

(6)

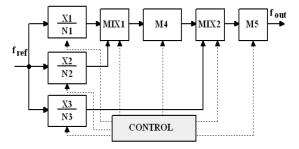

The block diagram of final version of frequency synthesizer with 3 "(X/N)" blocks is shown in Fig. 6. Output frequency of this synthesizer (for 3 blocks X/N) is given by equation:

$$f_{OUT} = (\frac{X_1}{N_1} + \frac{X_2}{N_2} + \frac{X_3}{N_3}) M_4 M_5 f_{REF}$$

(7)

Structure of synthesizer (Fig. 6) can be simply extended for more "(X/Y)" block.

Fig. 6. Final version of frequency synthesizer with 3 blocks (X/N). The blocks M4 and M5 are PLL which acts as multipliers and signal shape recover.

The  $N_1$ ,  $N_2$ ,  $N_3$  are fixed dividers and  $X_1$ ,  $X_2$ ,  $X_3$  are programmable dividers in PLL feedback. The  $M_4$  and  $M_5$  are also programmable dividers in feedback of PLL. These PLL are used for signal shape recover (from pulses to sine). Control block can be built with microcontroller or programmable array [10], [11].

### 3. MIXER BASED ON COINCIDENCE

As a review, let's look at an conventional analog mixer, which performs the function of multiplication between two inputs. Analog mixing implements the following trigonometric identity:

$$C = AB = \cos(2\pi f_a t)\cos(2\pi f_b t) =$$

$$= \frac{1}{2} [\cos(2\pi (f_a + f_b)t) + \cos(2\pi (f_a - f_b)t)]$$

(8)

and bandpass filtered output D (depend on filter quality):

$$D \approx \frac{1}{2} \left[ \cos(2\pi (f_a + f_b)t) \right] \tag{9}$$

There are some problems with filtering when frequencies  $(f_a + f_b)$  and  $(f_a - f_b)$  are close each other and tuning filter when frequency changing. Therefore new coincidence mixer was developed.

The new coincidence mixer work with input signals, which must have the same amplitude values.

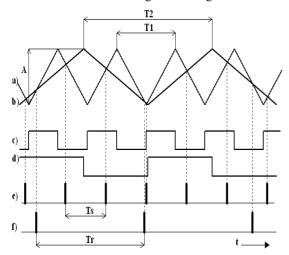

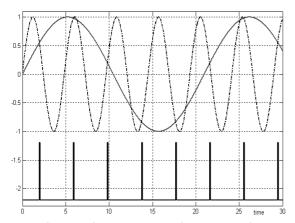

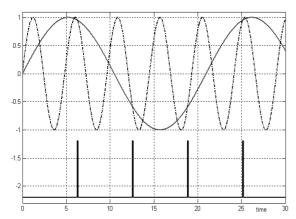

The new principle [12] is shown in Fig. 7, with triangle wave. The time diagrams of signals with sine wave are shown in Fig. 8. and Fig. 9.

Fig. 7. Coincidence mixer time diagram. a) input signal with frequency  $f_1$  (period  $T_1$ ), b) input signal with frequency  $f_2$  (period  $T_2$ ), c) derivation of signal a), d) derivation of signal b), e) output pulses with frequency  $f_S = f_1 + f_2$  (period  $T_S$ ) f) output pulses with frequency  $f_R$  =  $abs(f_1 - f_2)$  (period  $T_R$ )

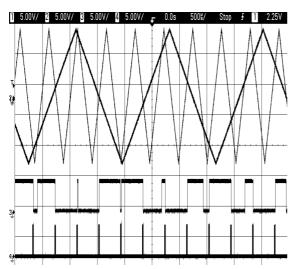

Fig. 8. Coincidence mixer time diagram (Simulation result). Input signals (top) and output pulses (bottom). Frequency of output pulses is sum of input frequencies.

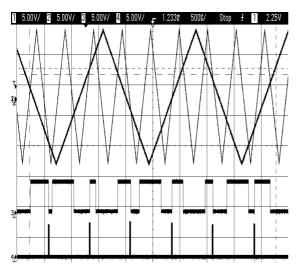

Fig. 9. Coincidence mixer time diagram (Simulation result). Input signals (top) and output pulses (bottom).

Frequency of output pulses is difference of input frequencies.

From Fig. 8 and 9 can be seen, that coincidence mixer can generate sum and difference of input frequencies on outputs, and outputs signals shapes are pulses. In Fig. 8 and 9, the frequency of input signals were 0.3 and 1.3 [rad/sec], therefore sum output is 0.3+1=1.6 and difference output is 1.3 - 0.3 =1 [rad/sec]. The simplified block diagram of coincidence mixer is shown in Fig. 10.

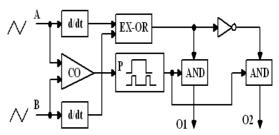

Fig. 10. Block diagram of coincidence mixer.

A, B - input signals, d/dt - derivation block,

CO - comparator, P - pulse block which generate pulse on rising and falling edge, EX-OR - exclusive-or gate,

AND - logical and gate, O1 - output with sum of input frequencies, O2 - output with difference of input frequencies.

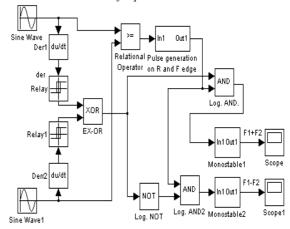

Fig. 11. Block diagram of coincidence mixer for Matlab simulation. The mixer has 2 output F1+F2 and absolute value of F1 - F2. The Relay blocks are used as a converter to digital signal level.

#### 4. SIMULATION RESULT, DISCUSSION

From simulation results shown in Fig. 8 and Fig. 9 can be seen, that mixer output pulses are equally spaced and therefore good spectral purity for sum and difference frequencies. The main drawback of this synthesizer is pulsed output and therefore PLL on output is need for recovery triangle or sine output. The second disadvantage is: The same amplitude of input signals is need. The first main advantage of this mixer is that no output filter is need and therefore it has a wide frequency bandwidth without any tuning. The second advantage is almost pure digital architecture (only comparator and derivation function are not pure digital). The third, sum and difference of frequencies can be simply generated. The block diagram of MATLAB simulation is shown in Fig. 11.

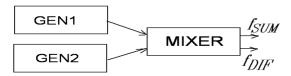

Fig. 12. The block diagram of mixer experimental measuring. GEN1 and GEN2 - functional generators, MIXER - coincidence mixer with f<sub>SUM</sub> and f<sub>DIF</sub> outputs.

# 5. EXPERIMENTAL RESULTS

The coincidence mixer was simulated and also constructed (according Fig. 10) and measured (according block diagram of Fig. 12). The two function generators GEN1 and GEN2 were used with triangle and sine signal outputs. The mixer has a 2 pulse outputs with sum of input frequencies  $f_{SUM}$  and difference of input frequencies  $f_{DIF}$ . The results with triangle signals are shown in Fig. 13 and 14.

Fig. 13. Top (1) and (2): Two triangle input signals with different frequencies  $f_1$  and  $f_2$ .

Middle (3): Output of analog comparator.

Botton (4): Output pulses with ouput frequency  $f_0 = f_1 + f_2$ .

Fig. 14. Top (1) and (2): Two triangle input signals with different frequencies  $f_1$  and  $f_2$ . Middle (3): Output of analog comparator. Botton (4): Output pulses with ouput frequency  $f_0 = |f_1 - f_2|$ .

#### 6. CONCLUSION

A detailed look at the concept of frequency synthesizer with new mixer, based on coincidence has been presented in this paper. Analysis, simulation and experimental results of the synthesizer were also shown.

# Acknowledgement

This research work has been supported by Department of Applied Electronics and Telecommunication, University of West Bohemia, Plzen, Czech Republic and from GACR (grant No. 102/07/0147).

# REFERENCES

- [1] EGAN, W. F. Frequency Synthesis by Phase Lock. 2nd ed. New York: Wiley, 1999.

- [2] BEST, R. E. *Phase-Locked Loops: Design, Simulation, and Applications*, 5th ed. New York: McGraw-Hill, 2003.

- [3] STENSBY, J, L. Phase-Locked Loops: Theory and Applications, CRC Press, USA, 1997, 382

- [4] MANASSEWITSCH, V. Frequency Synthesizers. 2rd ed., New York: Wiley, 1980, ISBN 0-471-07917-0

- [5] KROUPA, V. F. Close-to-the-carrier noise in DDFS, *IEEE Int. Freq. Contr. Symp.*, 1996, pp. 934-941.

- [6] KROUPA, V. F. Spectra of pulse rate frequency synthesizers, *Proc. IEEE*, *vol. 676*, pp.1680-1682, Dec. 1979.

- [7] KROUPA, V. F. Direct Digital Frequency Synthesizers, New York, IEEE Reprint Press Book, 1998.

- [8] VANKKA, J, WALTARI, M, KOSUNEN, HALONEN, K, I, A Direct Digital Synthesizer with an On-Chip D/A-Converter, *IEEE Journal* of Solid-State Circuits, Vol. 33, No. 2, pp. 218-227, February 1998.

- [9] FLATH, D, E. *Introduction to Number Theory*, New York: Wiley, 1989.

- [10] GOLDBERG, B. G. Digital Techniques in Frequency Synthesis, New York: McGraw-Hill, 1995.

- [11] ROHDE, U, L. Microwave and Wireless Synthesizers: Theory and Design, John Wiley & Sons, Inc., USA, 1997, 638 p.

- [12] Stork, M: Koincidenční syntezátor frekvence. Užitný vzor č. 16557, r. 2006. (In Czech).